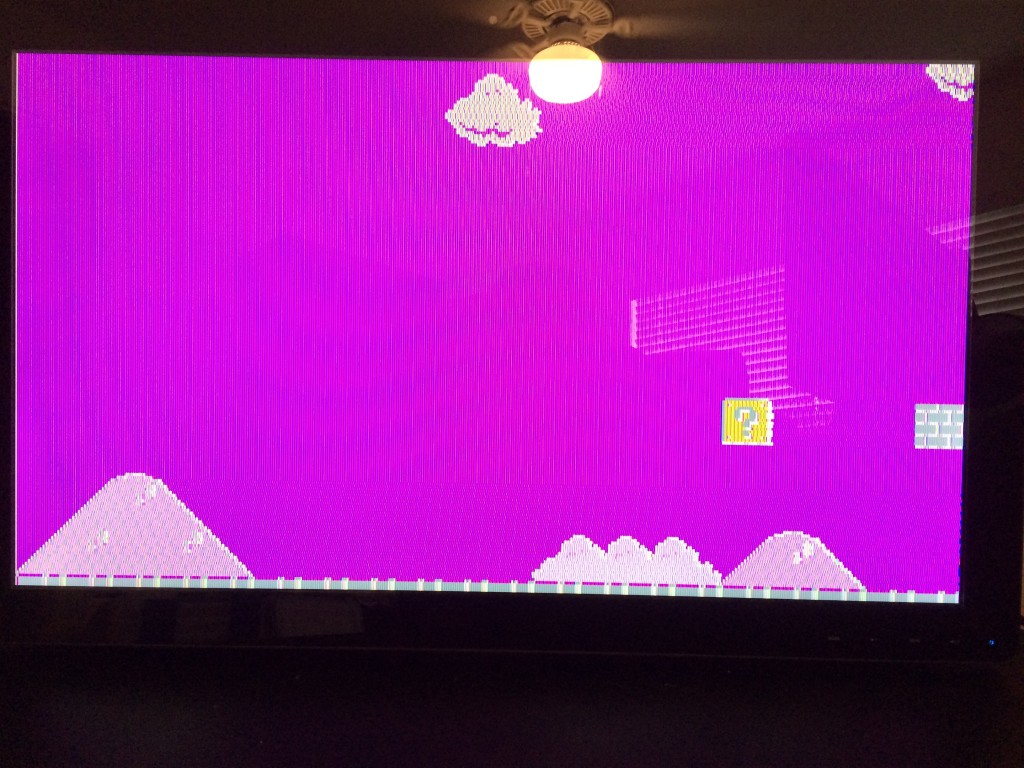

Plus a modicum of success. Let’s start with the more interesting of the two, glitches. This first one is is actually the first image I got with the board. Here the data going to the dvi serializes was bit swapped, causing all the colors to be wrong.

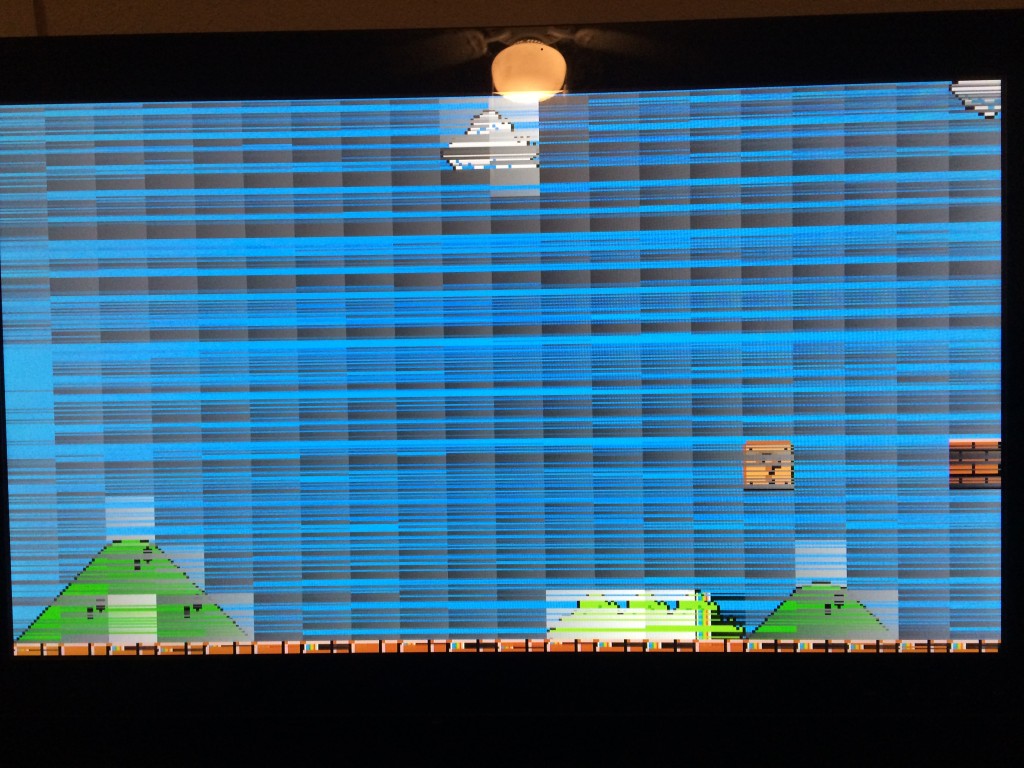

Here is a video of the glitch I mentioned in a previous post. This actually turned out not to be a glitch in the logic clock as I originally thought. What was happening is the frame and line start pulses are generated off the dvi clock and then cross to the logic clock domain. Both pulses happen on the same clock in the dvi domain and the logic domain expects the frame start pulse to occur at or before the first line start pulse. But for some reason the frame start pulse would cross one clock after the line start pulse. This prevents the map pointer from resetting to the beginning of the map data. Instead the map pointer just kept incrementing, into uninitialized data. I moved the frame start pulse one line back to fix it.

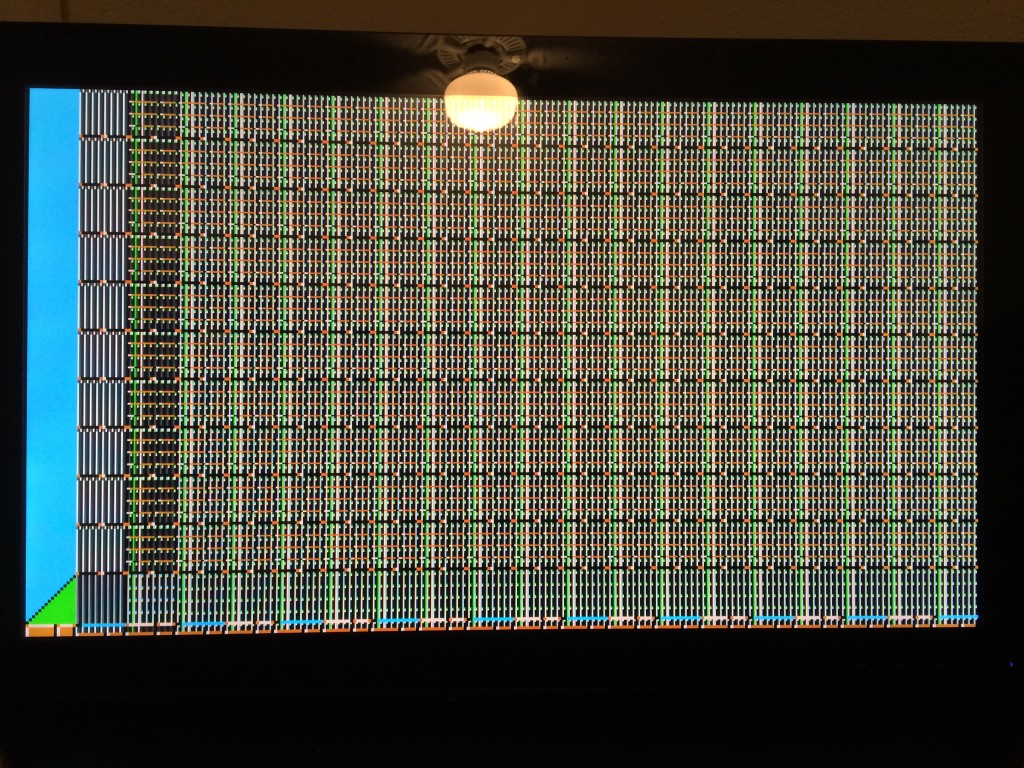

These next images are side effects of me fussing with the SRAM controller trying to get rid of the above glitch before I realized what was going on. I basically re-wrote the controller a few times with varying ratios of registered and combinational logic. I ended up sticking mostly with my original registered design, but with the SRAM clock shifted 180 degrees out of phase.

And lastly here’s a video of everything mostly working. Boring I know. I’m scrolling the map with a SNES controller (the config interface is working now) and the audio unit is also playing a midi in the background, so the delta sigma DAC is confirmed working. The audio is quiet so it’s hard to hear, deal with it.

Lessons learned: metastability is a pain, even if compensated for crossing clock domains isn’t perfect. Gotta pack those IOBs.